E-Books / Video Training →Simple Axi Bus Design Using Verilog Hdl

Published by: voska89 on 30-12-2023, 23:42 |  0

0

Free Download Simple Axi Bus Design Using Verilog Hdl

Published 12/2023

MP4 | Video: h264, 1920x1080 | Audio: AAC, 44.1 KHz

Language: English | Size: 595.23 MB | Duration: 1h 4m

AXI in easy understand

What you'll learn

Concept of AMBA bus protocol

Concept of AXI Bus

Design and implementation of AXI bus using Verilog HDL

Verification of AXI bus

Requirements

Verilog HDL

Description

AMBA is an open standard for SoC design created by Arm to allow for high-performance, modular, and reusable designs that work right the first time while minimizing both power and silicon. This course discusses the AMBA, which introduced the Advanced Extensible Interface (AXI) protocol.Originally conceived for high-frequency systems, the AXI protocol was designed to meet the interface requirements for a wide range of components, while allowing for flexibility in how those components are interconnected. Suitable for high-frequency, low-latency designs, AXI remains backward compatible with the AHB and APB from the previous AMBA revision.Understanding AXI will give you deep insight into how an SoC works while making you a versatile and well-rounded designer. Recall that the AHB (Advanced High-Performance Bus) is a single-channel bus that multiple masters and slaves use to exchange information. A priority arbiter determines which master currently gets to use the bus, while a central decoder performs slave selection. Operations are performed in bursts that can take multiple bus cycles to complete. Every burst transfer consists of an address and control phase followed by a data phase. AXI was designed with a similar philosophy but uses multiple, dedicated channels for reading and writing. AXI is burst-based like its predecessor and uses a similar address and control phase before data exchange. AXI also includes several new features including out-of-order transactions, unaligned data transfers, cache support signals, and a low-power interface. You can refer to AMBA AXI Protocol v1.0 for a deeper look into the AXI.

Overview

Section 1: Course Introduction

Lecture 1 Introduction

Lecture 2 AMBA introduction

Lecture 3 Comparision between AHB, AXI, APB

Section 2: AXI bus

Lecture 4 Introduction to AXI

Lecture 5 AXI channel Architecture of Read/writes

Lecture 6 AXI signals

Lecture 7 Handshaking signals

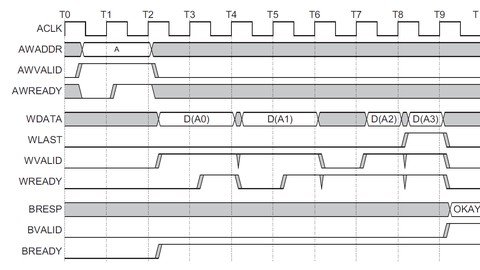

Lecture 8 Signal Diagram

Lecture 9 Write process Timing diagram

Lecture 10 Read process Timing diagram

Lecture 11 Dependencies between channel handshake signals

Section 3: Implementation of Simple AXI bus

Lecture 12 AXI state machine for write & read

Lecture 13 AXI Master/Slave Block diagram and Write/read process

Section 4: Source code

Lecture 14 Design of AXI bus using verilog HDL- write process

Lecture 15 Design of AXI bus using verilog HDL- Read process

Lecture 16 AXI master & slave

Lecture 17 Test bench & simulation

Intermediate level people who planning to going for job

Homepage

https://www.udemy.com/course/simple-axi-bus-design-using-verilog-hdl/Buy Premium From My Links To Get Resumable Support,Max Speed & Support Me

Rapidgator

jloaz.Simple.Axi.Bus.Design.Using.Verilog.Hdl.rar.html

Uploadgig

jloaz.Simple.Axi.Bus.Design.Using.Verilog.Hdl.rar

NitroFlare

jloaz.Simple.Axi.Bus.Design.Using.Verilog.Hdl.rar

Fikper

jloaz.Simple.Axi.Bus.Design.Using.Verilog.Hdl.rar.html

No Password - Links are Interchangeable

Related News

-

{related-news}